メモリーインターリーブとは何か

― 教科書どおりに理解する ―

はじめに

基本情報技術者試験や職業訓練校の教材では、

主記憶装置の高速化技術として メモリーインターリーブ が登場します。

教科書では次のように説明されています。

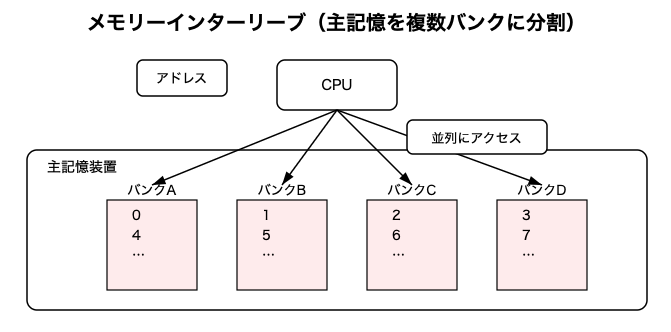

メモリーインターリーブとは、CPUから主記憶装置へのアクセスを高速化するために、主記憶装置内部を複数のバンクに分割し、各バンクに並列にアクセスする方式である。

この記事では、この 教科書の説明に沿ってメモリーインターリーブの考え方を整理します。

メモリーインターリーブの基本的な考え方

主記憶装置へのアクセスは、CPUの処理速度と比べると遅く、その待ち時間が性能低下の原因になります。

そこで用いられるのが メモリーインターリーブ です。

ポイントは次の2点です。

- 主記憶装置を 複数のバンク に分ける

- 複数のバンクに 並列にアクセス する

これにより、主記憶装置へのアクセスが高速化されます。

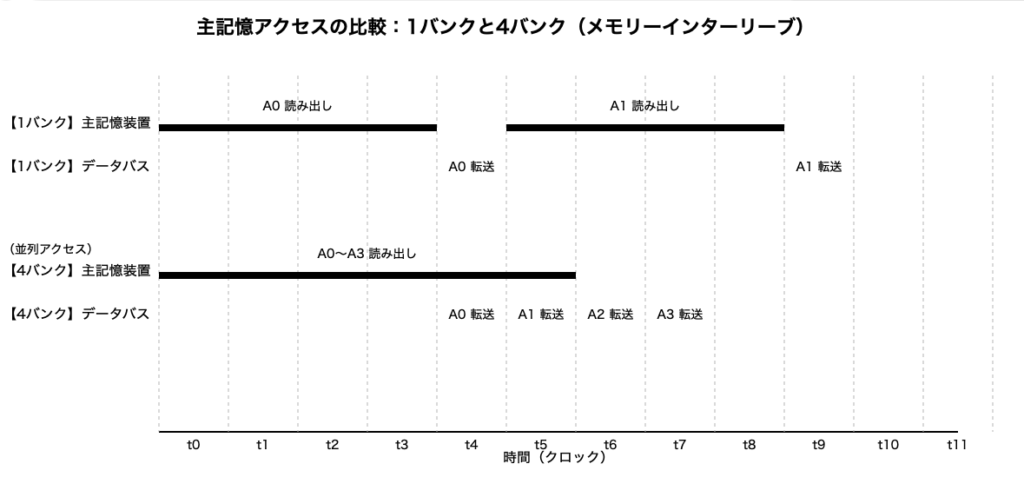

1バンクの場合

まず、主記憶装置が 1つのバンク しか持たない場合を考えます。

- CPUは、1つのバンクに対して順番にアクセスする

- 次のデータを取得するまで、待ち時間が発生する

このように、アクセスが 直列的 になるため、CPUは待たされる時間が多くなります。

複数バンク(インターリーブ)の場合

次に、主記憶装置を 複数のバンク に分けた場合です。

例えば、4バンク構成では、

- 主記憶装置がバンクA・バンクB・バンクC・バンクDに分割されている

- CPUは、これらのバンクに 並列にアクセス できる

この結果、

- あるバンクにアクセスしている間に

- 別のバンクにもアクセスできる

ようになり、待ち時間が減少 します。

図で見る:1バンクと4バンクの比較

- 1バンク構成→ アクセスが直列になり、待ち時間が多い

- 4バンク構成(メモリーインターリーブ)→ 複数バンクに並列アクセスでき、待ち時間が少ない

図に書いている 「図では「読み出し」と書いていますが、これは「読み出し命令を出して、準備している時間だと思ってください。

実際のデータは、少し後でバスを通って届きます。

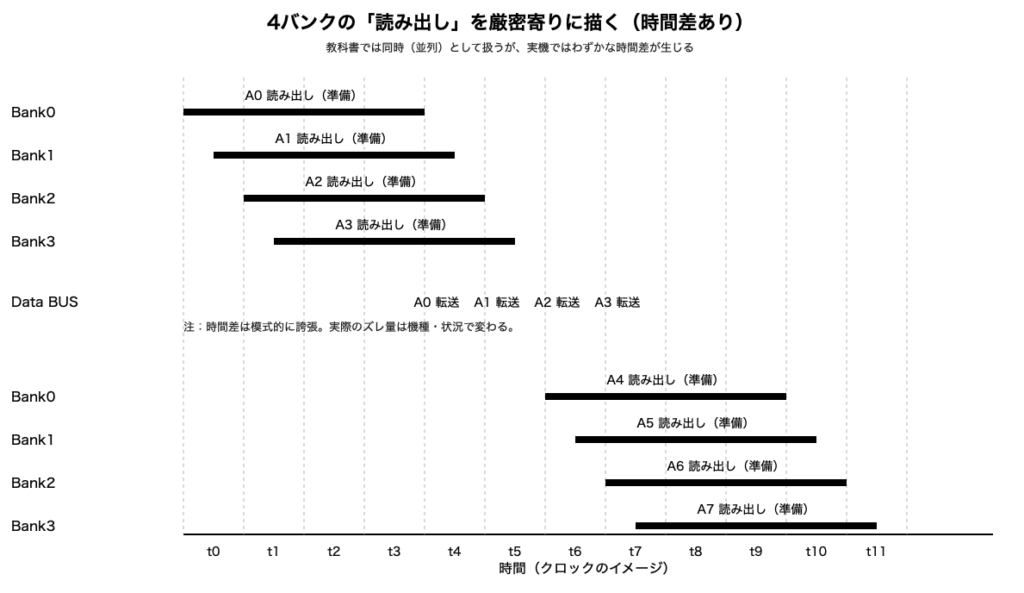

厳密に言うと「時間差はあります」

ただし、教科書レベルでは無視してよい差です。ここを切り分けて説明します。

結論(短く)

- 厳密には4バンクの A0〜A3 の読み出しは完全な同時開始ではなく、わずかな時間差があります。

- 教科書・試験レベルでは「並列に読み出している」と考えて問題ありません。

なぜ時間差が生じるのか(厳密な話)

4バンクといっても、現実のハードウェアでは:

- CPU(メモリコントローラ)がアドレス要求を 順に発行する

- 各バンクがそれぞれのタイミングで内部動作を開始する

ため、

- Bank0 → Bank1 → Bank2 → Bank3と 数クロック未満のズレが生じます。

これは、

- コマンド発行順

- 内部配線

- タイミング制約

によるものです。

それでも「並列」と呼ぶ理由

重要なのはここです。

- 1バンクの場合→ 前の読み出しが完全に終わるまで次に進めない

- 4バンクの場合→ 前の読み出しが進行中でも、次のバンクを動かせる

つまり、

処理が重なって進行している

という意味で「並列」と呼んでいます。

図との関係(今回の図は正しいか)

今回作成した図では:

- A0〜A3 の読み出しを同一の横バーで表現

していますが、これは:

- 教科書どおりの抽象化

- 試験対策として正しい表現

です。

もし厳密に描くなら:

- A0, A1, A2, A3 のバーを少しずつずらして重ねる

形になります。

1つのバンクを取り出して比較

4バンクの場合

まとめ

- 4バンクの読み出しは完全同時ではない

- しかし重なって進行する

- そのため「並列アクセス」と表現する

「並列にアクセスする」とはどういう意味か

教科書でいう 「並列にアクセスする」 とは、

- CPUが主記憶装置内部の複数バンクに対して

- 同時にアクセス要求を出せる

という意味です。

これにより、アクセスの重なりが生まれ、全体として高速になります。

試験で押さえるポイント

基本情報技術者試験では、

メモリーインターリーブについて次の点を理解していれば十分です。

- 主記憶装置を複数のバンクに分割する

- 各バンクに並列にアクセスすることで高速化する

- 主記憶装置のアクセス時間短縮が目的である

細かな内部構造まで理解する必要はありません。

実効アクセス時間との関係

試験では、キャッシュメモリと組み合わせて実効アクセス時間 を計算する問題がよく出題されます。

この場合、

- キャッシュヒット時は高速

- ミス時は主記憶装置にアクセス

という前提で、次の式を用います。

実効アクセス時間 = キャッシュメモリのアクセス時間 × ヒット率 + 主記憶装置のアクセス時間 ×(1 − ヒット率)

メモリーインターリーブは、この 主記憶装置のアクセス時間を短縮する技術 の一つです。

まとめ

- メモリーインターリーブは、主記憶装置の高速化技術である

- 主記憶装置を複数のバンクに分割する

- 各バンクに並列にアクセスすることで待ち時間を減らす

- 試験では教科書の説明どおり理解すればよい

一文で覚えるなら

メモリーインターリーブとは、主記憶装置を複数のバンクに分割し、並列にアクセスすることで高速化する方式である。

ディスカッション

コメント一覧

まだ、コメントがありません